# System for Acquisition of Corneal Images Slip Lamp Application

Thesis by

# Hugo José Pinto de Almeida

In Fulfillment of the Requirements

for

Master's Degree in Biomedical Engineering

Coimbra, September 2012 (defended September 24)

This work is funded by FEDER, through the Programa Operacional Factores de Competitividade-COMPETE and by National funds through FCT- Fundação para a Ciência e Tecnologia in the frame of project PTDC/SAU-BEB/104183/2008, F-COMP-01-0124-FEDER-010941

Este trabalho é financiado pelo FEDER, através do Programa Operacional Factores de Competitividade-COMPETE e fundos nacionais através da FCT- Fundação para a Ciência e Tecnologia no âmbito do projeto PTDC/SAU-BEB/104183/2008, F-COMP-01-0124-FEDER-010941

Esta cópia da tese é fornecida na condição de que quem a consulta reconhece que os direitos de autor são pertença do autor da tese e que nenhuma citação ou informação obtida a partir dela pode ser publicada sem a referência apropriada.

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognize that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without proper acknowledgement.

All contents written in Portuguese are in compliance with Old Portuguese Language Orthographic Agreement.

Accepted by the University of Coimbra, in fulfillment of the requirements for the degree of Master in Biomedical Engineering.

| (PhD) Custódio Francisco Loureiro Melo <sup>1,2</sup> ( <b>Chairperson</b> ) |

|------------------------------------------------------------------------------|

| (PhD) Francisco José Amado Santiago Fernandes Caramelo                       |

| (PhD) José Paulo Pires Domingues <sup>1,3</sup> ( <b>Advisor</b> )           |

Thesis Examination Committee:

<sup>&</sup>lt;sup>1</sup>Department of Physics, Faculty of Sciences and Technology, University of Coimbra, Portugal <sup>2</sup>Instrumentation Center, Faculty of Sciences and Technology, University of Coimbra, Portugal <sup>3</sup>IBILI – Institute of Biomedical Research in Light and Image, Faculty of Medicine, University of Coimbra, Portugal

# Acknowledgements

Começo por agradecer a toda a equipa do projecto NeuroCórnea, em particular ao Professor Doutor José Paulo Domingues, meu orientador de projecto, pelo acompanhamento prestado durante todo o ano.

Agradeço aos meus avós paternos por estarem presentes na minha vida, não só nesta fase mas no passado e daqui adiante.

Ao Maurício (palmas ao malabarista) e à Carlota (com um beijo), que me acompanharam de perto durante o decorrer do projecto e a escrita da tese, agradeço pelos bons momentos.

Aos meus pais, muitíssimo obrigado por todo o esforço e dedicação que possibilitou a minha caminhada pelo percurso universitário. Esta tese é-lhes dedicada.

A todos, agradeço.

#### Abstract

Diabetes is a chronic disease that is associated chronic complications such as diabetic neuropathy - leading cause of disability in diabetics.

Currently, corneal confocal microscopy is a technique used to acquire *in vivo* images of the cornea nerves. As an expensive technology which is only available in central hospitals and private clinics, the case of a slit lamp microscope is a starting point to improve this solution since it is often used to observe the anterior segment of the eye. Thus, the purpose of NeuroCórnea is (but not only) the development of a confocal module for use in a slit lamp microscope; a method for assessing the corneal nerves for diagnosis and monitoring of diabetic neuropathy.

A part of the object of NeuroCórnea has to do light intensity measurement. In order to achieve part of this goal, has been proposed an acquisition model based on a Hamamatsu FFT-CCD C5809 Image Sensor and controlled by a PIC microcontroller. Due to a failure that arose during the project, the FFT-CCD was replaced by a S3921-128Q MOS Linear Image Sensor, which would be the only way to continue to get results.

During the course of the project we were given the opportunity to work with LIP-Coimbra (Laboratory of Instrumentation and Experimental Physics of Particles) and adapting our entire system (hardware, firmware and software) for a temperature measurement system for a liquid xenon detector. This was not an objective proposed in the beginning but served to consolidate knowledge and show the versatility of the instrumentation.

In order to handle all these devices (PIC, FFT-CCD, MOS and LIP circuit) was created a GUI (Graphical User Interface) using *Microsoft Visual Studio C++* that has, among other features, the ability to view real-time video outputs for each device.

In short, this project was handling a wide range of variables such as: electronic components (regulators, references, ADC ...), PIC microcontroller, graphical interface (GUI), C programming language (C and Visual C++), Assembler programming language, handling various tools (an example is welding with tin). In the end, the knowledge gained was successful and personally rewarding.

Keywords: Cornea, diabetic neuropathy, FFT-CCD, PIC microcontroller, MOS, LIP.

#### Resumo

A diabetes é uma doença crónica que tem associadas complicações como por exemplo a neuropatia diabética – maior causa de incapacidade em diabéticos.

Actualmente, a microscopia confocal da córnea é a técnica usada para adquirir imagens dos nervos da córnea *in vivo*. Sendo uma tecnologia onerosa e que só está disponível em hospitais centrais e clínicas privadas, o caso do microscópio de lâmpada de fenda é um ponto de partida para melhorar esta solução uma vez que é frequentemente usado para observar o segmento anterior do olho humano. Assim, o propósito da NeuroCórnea é (mas não só) o desenvolvimento de um módulo confocal para aplicação num microscópio de lâmpada de fenda. É um método para avaliação dos nervos da córnea, para o diagnóstico e acompanhamento da neuropatia diabética.

Uma parte do objectivo da NeuroCórnea tem que ver com a medição da intensidade. De modo a cumprir uma parte deste objectivo foi proposto um modelo de aquisição baseado num sensor de imagem FFT-CCD C5809 da Hamamatsu e comandado por um microcontrolador PIC. Devido a uma avaria que surgiu no decorrer do projecto, o sensor FFT-CCD foi trocado por um sensor de imagem linear S3921-128Q MOS, que seria o único modo de prosseguir para obter resultados.

Durante o decorrer o projecto foi-nos dado a oportunidade de trabalhar com o LIP-Coimbra (Laboratory of Instrumentation and Experimental Physics of Particles) num sistema de medição de temperatura para uma câmara de xénon líquido e, adaptando todo o nosso sistema (hardware, firmware e software), conseguimos atingir o objectivo proposto. Este não era um objectivo proposto no início mas serviu para consolidar conhecimentos e mostrar a versatilidade da instrumentação.

De modo a manipular todos estes dispositivos (PIC, FFT-CCD, MOS e circuito do LIP) foi criada uma interface gráfica usando o *Microsoft Visual Studio C++* que tem, entre outras funcionalidades, capacidade de visualizar em tempo real as saídas vídeo de cada dispositivo.

Em suma, neste projecto houve manipulação de uma pluralidade de variáveis tais como: componentes electrónicos (reguladores, referências, ADC...), microcontroladores PIC, linguagens de programação C (Visual C++ e C), interface gráfica, linguagem de programação Assembler, manuseamento de vários instrumentos (um exemplo é a soldadura com estanho)... No fim, a aprendizagem obtida foi pessoalmente gratificante.

**Palavras-chave**: Córnea, neuropatia diabética, FFT-CCD, microcontrolador PIC, MOS, LIP.

# **Table of Contents**

| Acknowledge     | ements                                                   | v    |

|-----------------|----------------------------------------------------------|------|

| Abstract        |                                                          | vi   |

| Resumo          |                                                          | vii  |

| Table of Cont   | ntents                                                   | viii |

| List of Figures | es                                                       | xi   |

| List of Tables  | S                                                        | xii  |

| List of Examp   | ples                                                     | xii  |

| Chapter 1.      | Introduction                                             | 1-1  |

| 1.1 - Diabe     | petic Neuropathy                                         | 1-1  |

| 1.2 - Neuro     | roCórnea                                                 | 1-1  |

| 1.3 - Objec     | ective                                                   | 1-2  |

| 1.4 - Micro     | ocontrollers                                             | 1-2  |

|                 | PIC                                                      |      |

| 1.5 - Von N     | Neumann Architecture                                     | 1-4  |

| 1.6 - Harva     | vard Architecture                                        | 1-4  |

| 1.7 - Modij     | lified Von Neumann Architecture and Harvard Architecture | 1-5  |

| Chapter 2.      | PIC32 USB Starter Kit II Microchip                       | 2-1  |

| 2.1 - PIC32     | 2MX (PIC32MX795F512L)                                    | 2-2  |

| 2.1.1 - Ir      | Interrupts                                               | 2-2  |

|                 | 1.1 - Interrupt Priorities and Sub Priorities            |      |

| •               | I/O Ports                                                |      |

|                 | 2.1 - Control Registers                                  |      |

|                 | 2.2 - Modes of Operation                                 |      |

|                 | Timers                                                   |      |

|                 | 3.1 - Control Registers                                  |      |

|                 | 3.2 - Interrupt Configuration                            |      |

|                 | Output Compare                                           |      |

|                 | Expansion Board                                          |      |

|                 |                                                          |      |

| Chapter 3.      | Power Supply Voltage Board                               | 3-1  |

| 3.1 - PT78I     | BNR115S (-15V)                                           | 3-2  |

| 3.2 - L7812     | 12CV (+12V)                                              | 3-2  |

| 3.3 - LM78      | 815CV (+15V)                                             | 3-2  |

| 3.4 - LM78      | '8M05CT (+5V)                                            | 3-3  |

| 3.5 - LD108     | 085V50 (+5V)                                             | 3-3  |

| 3.6 - IE122     | 24S (+24V)                                               | 3-4  |

| 3.8 - PTN78000A (-15V)                                                          | 3-5 |

|---------------------------------------------------------------------------------|-----|

| 3.7 - REF 195                                                                   | 3-5 |

| 3.8 - 16-bit ADC AD7680                                                         | 3-6 |

| Chapter 4. Hamamatsu Image Sensors                                              | 4-1 |

| 4.1 - FFT-CCD C5809 Image sensor                                                | 4-1 |

| 4.1.1 - Timing signal generator                                                 |     |

| 4.1.2 - Voltage regulators                                                      |     |

| 4.1.3 - Inputting the control signal from the PIC (Start and CLK)               |     |

| 4.2 - S3921-128Q MOS Linear Image Sensor                                        |     |

| 4.2.1 - Driver Circuit                                                          |     |

| 4.2.1 - Signal Readout Circuit                                                  |     |

| Chapter 5. Temperature Monitor for a Liquid Xenon Detector                      |     |

| 5.1 - LIP - Laboratory of Instrumentation and Experimental Physics of Particles |     |

| , -                                                                             |     |

| 5.2 - 1N4148 diodes                                                             |     |

| ·                                                                               |     |

| 5.3 - PCB                                                                       | 5-2 |

| 5.4 – LIP circuit                                                               | 5-3 |

| Chapter 6. Firmware                                                             | 6-1 |

| 6.1 - Introducing MPLAB                                                         | 6-1 |

| 6.2 - The elements of MPLAB                                                     | 6-1 |

| 6.3 - MPLAB C32 C Compiler                                                      | 6-2 |

| 6.3.1 - File Naming Conventions                                                 | 6-2 |

| 6.3.1.1 - Data Storage                                                          | 6-2 |

| Storage Endianness                                                              | 6-2 |

| Integer Representation                                                          | 6-2 |

| Signed and Unsigned Character Types                                             | 6-3 |

| Floating-Point Representation                                                   |     |

| 6.3.2 - Pragmas (pragmatic information)                                         |     |

| 6.3.3 - Interrupts                                                              |     |

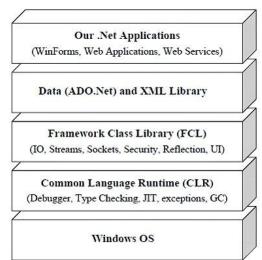

| Chapter 7. Software                                                             | 7-1 |

| 7.1 - Visual C++/CLI                                                            | 7-1 |

| 7.1.1NET                                                                        |     |

| 7.1.2 - Framework .NET                                                          |     |

| 7.1.3 - Common Language Runtime                                                 |     |

| 7.2 - Windows Forms                                                             |     |

| Chapter 8. Results                                                              | 8-1 |

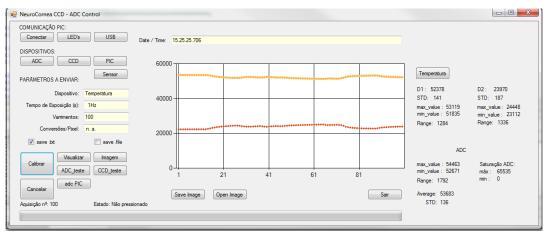

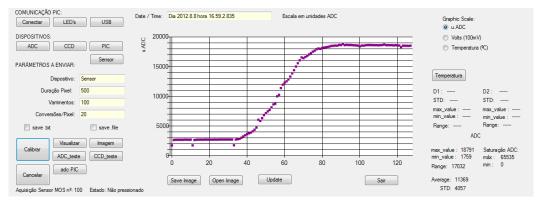

| 8.1 - The graphical interface (GUI)                                             | 8-1 |

| 8.1.1- Communication between Forms                                              |     |

| 8.2 - Data Visualization                                                        | 8-2 |

| 8.2.1 - Save data in .txt format                                                | 8-2 |

| 8.3 - Communication between PC and PIC                                          |     |

| 8.3.1 - Sending Data to PIC Firmware                                            |     |

| 8.3.2 - Sending Data to PC Software                                             | 8-4 |

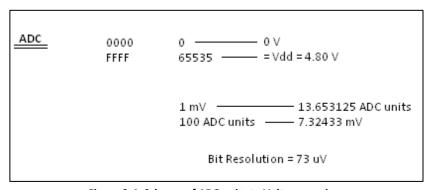

| 9.3.2.1 - How conversions are made                                              | 8-5 |

| 8.4 - ADC Tests                                                  | 8-6  |

|------------------------------------------------------------------|------|

| 8.4.1 - Effective number of bits (ENOB) of the 16-bit ADC AD7680 | 8-6  |

| 8.1.1.1 - 1.3 Volts battery test                                 | 8-7  |

| 8.4.2 - ADC units to Volts conversion                            | 8-8  |

| 8.4.3 - SPI communication                                        | 8-9  |

| 8.5 - FFT-CCD image sensor                                       | Q_10 |

| 8.5.1 - External control signals                                 |      |

| 8.5.2 - Acquisition parameters                                   |      |

| 8.5.3 - Disk storage                                             |      |

| 8.5.4 - Processing of Data                                       |      |

| 8.6 - LIP – Temperature Monitor for Liquid Xenon Detector        |      |

|                                                                  |      |

| 8.7 - MOS Linear Image Sensor                                    |      |

| 8.7.1 - External control signals                                 |      |

| 8.7.2 - A/D Conversion                                           |      |

| 8.7.3 - Pixel duration time                                      | 8-16 |

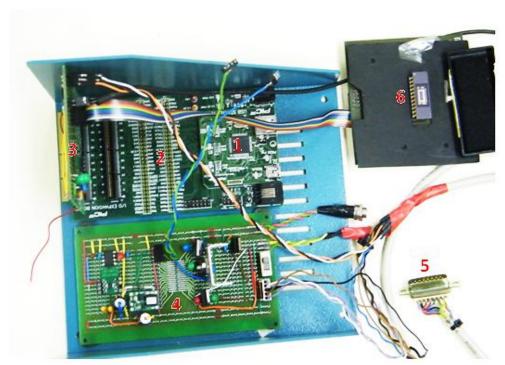

| 8.8 - Final prototype                                            | 8-17 |

| 8.9 - Unsolved problems                                          | 8-18 |

| Chapter 9. Conclusion and Future work                            | 9-1  |

| Bibliography                                                     |      |

|                                                                  |      |

| Attachment I                                                     | A    |

|                                                                  |      |

| Attachment II                                                    | В    |

| Attachment III                                                   | C    |

|                                                                  |      |

| Attachment IV                                                    | D    |

| Attachment V                                                     | -    |

| Attaciment v                                                     | E    |

| Attachment VI                                                    | F    |

|                                                                  |      |

| Attachment VII                                                   | G    |

| Attachment VIII                                                  | Ц    |

| Attaciment viii                                                  | П    |

| Attachment IX                                                    |      |

|                                                                  |      |

| Attachment X                                                     | J    |

|                                                                  |      |

| Attachment XI                                                    | K    |

|                                                                  |      |

| Attachment XII                                                   | L    |

| Attachment XIII                                                  | N // |

| ALIGUIIIIEIIL AIII                                               | IVI  |

| Attachment XIV                                                   | N    |

# **List of Figures**

| Figure 1-1. Zilog Z80 - 8-bit microprocessor designed and sold by Zilog from July 1976. [7]                     | _ 1-2        |

|-----------------------------------------------------------------------------------------------------------------|--------------|

| Figure 1-2. The Von Neumann architecture. [10]                                                                  | _ 1-4        |

| Figure 1-3. The Harvard architecture. [10]                                                                      | _ 1-5        |

| Figure 2-1. PIC32 USB Starter Kit II. [13]                                                                      | _ 2-1        |

| Figure 2-2. Interrupt Controller Module                                                                         | _ 2-2        |

| Figure 2-3. The Starter Kit I/O Expansion Board.[14]                                                            | _ 2-8        |

| Figure 2-4. Microchip PICtail Plus Daughter Board.                                                              | _ 2-8        |

| Figure 3-1. Board with power supplies for the Hamamatsu FFT-CCD C5809 Image Sensor                              | _ 3-1        |

| Figure 3-2. Standart Application, Pin-Out Information and Ordering Information of PT78NR100                     |              |

| Series. [16]                                                                                                    | _ 3-2        |

| Figure 3-3. Connection Diagram (top view) and Standart Application Circuits of the L7800 series                 |              |

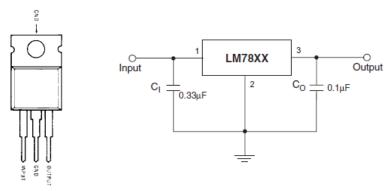

| regulators.[17]                                                                                                 | _ 3-2        |

| Figure 3-4. Connection Diagram (top view) and Standart Application Circuits of the LM7800 series                | S            |

| regulators.[18]                                                                                                 | _ 3-3        |

| Figure 3-5. Connection Diagram of the LM78M05CT regulator.[19]                                                  | _ 3-3        |

| Figure 3-6. Pin Configuration (top view) and Application Circuit of the LD1085V50 regulator. [20]               | _ 3-4        |

| Figure 3-7. Image and pinout of IE1224S DC/DC Converter.[21]                                                    | _ 3-4        |

| Figure 3-8. Standard Application of PTN78000A regulator. Application Information in Attachment                  |              |

| V.[23]                                                                                                          | _ 3-5        |

| Figure 3-9. Typical Connection Diagram of the REF195. [22]                                                      | _ 3-5        |

| Figure 3-10. Functional Block Diagram and Pin Configuration of 16-Bit AD7680. [22]                              | _ 3-6        |

| Figure 4-1. Timing diagram for drive circuit of S3921-128Q MOS Linear Image Sensor [28].                        | _ 4-3        |

| Figure 4-2. Recommend readout circuit and pulse timing for S3921-128Q MOS Linear Image                          |              |

| Sensor.[28]                                                                                                     | _ 4-4        |

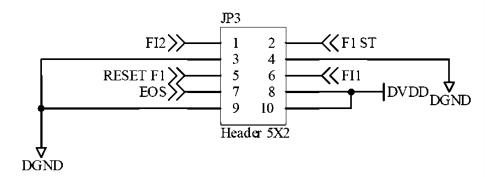

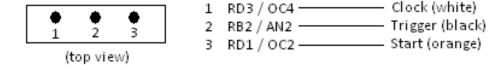

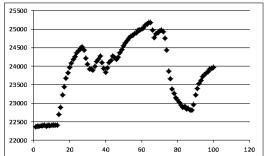

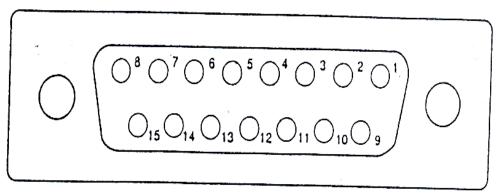

| Figure 4-3. Header for communication between MOS and PIC.                                                       | _ 4-4        |

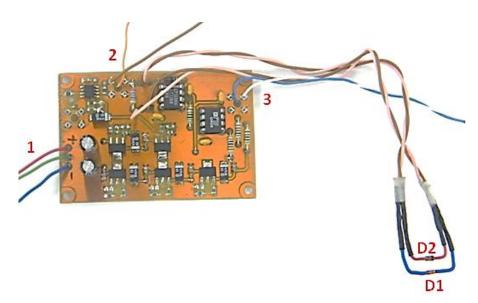

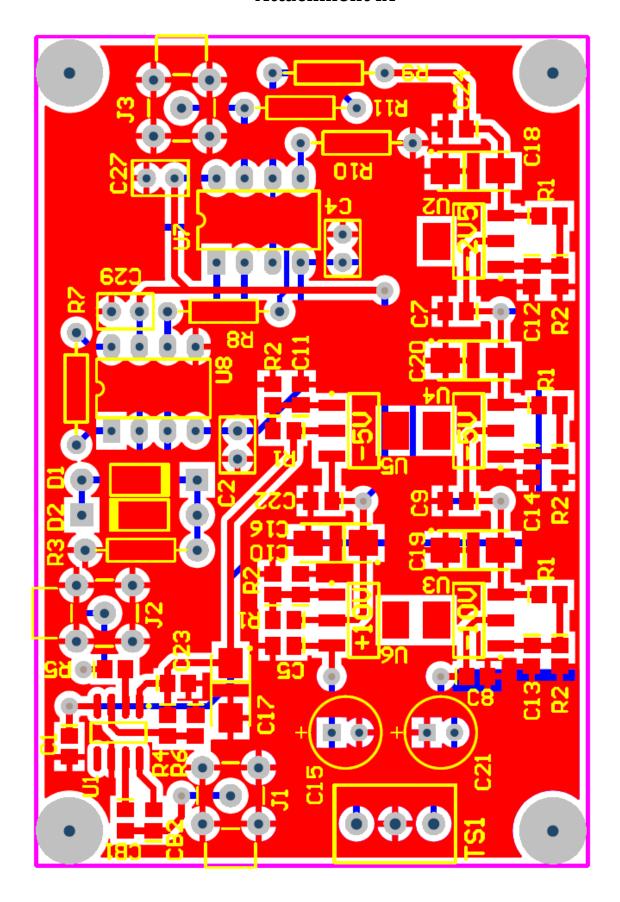

| Figure 5-1. PCB used to measure the temperature of the D1 and D2 diodes.                                        | _ 5-2        |

| Figure 5-2. Schematic of the circuit that will monitor the temperature of a liquid xenon detector.              |              |

| Figure 7-1. Framework .NET architecture diagram.                                                                | _ 7-1        |

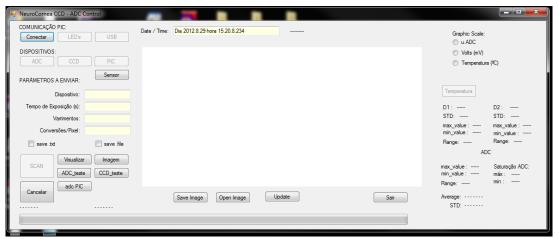

| Figure 7-2. Image of the first Form of the graphical user interface (GUI).                                      | _ 7-3        |

| Figure 8-1. Communication between two Windows Forms                                                             | _ 8-1        |

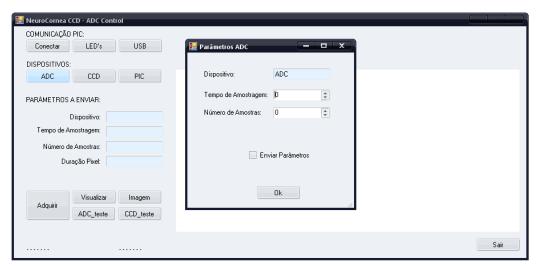

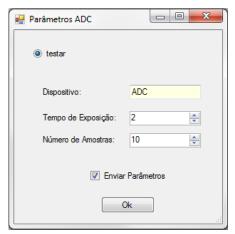

| Figure 8-2. ADC <i>WindowsForm</i> image where the ADC parameters are selected.                                 | _ 8-6        |

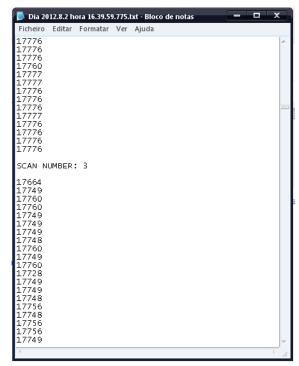

| Figure 8-3txt file that demonstrates a slight increase of values of SCAN NUMBER: 3 in relation t                |              |

| the SCAN NUMBER: 2.                                                                                             | _ 8-8        |

| Figure 8-4. Scheme of ADC units to Volt conversion.                                                             | _ 8-8        |

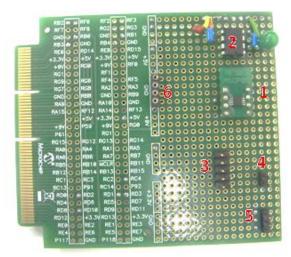

| Figure 8-5. Microchip PICtail Plus Daughter Board with components.                                              | _ 8-9        |

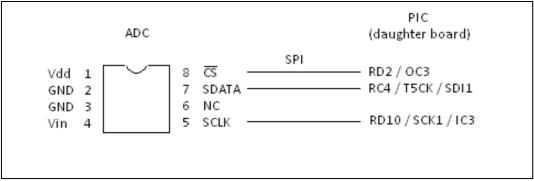

| Figure 8-6. Schematic of the correspondence between ADC pins and PIC pins.                                      | _ 8-9        |

| Figure 8-7. Header (in PIC daughter board) for connecting the Start and Clock signals FFT-CCD im-               | _            |

| 50 0 <u></u>                                                                                                    | 8-10         |

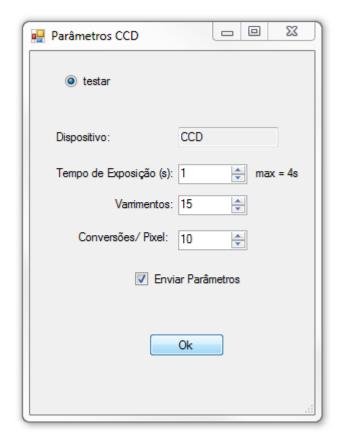

| 0 1                                                                                                             | 8-11         |

|                                                                                                                 | 8-12         |

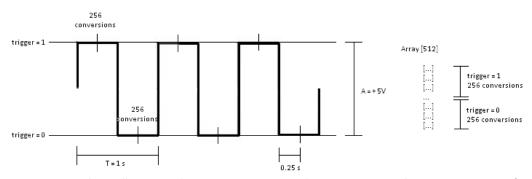

| Figure 8-10. Scheme illustrating the 1 Hz square wave used as a trigger to synchronize conversion               |              |

|                                                                                                                 | 8-13         |

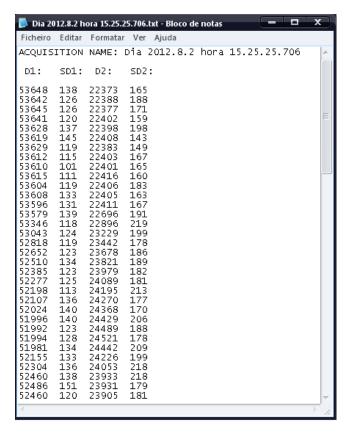

| Figure 8-11. File in ASCII format which are stored the mean values and standard deviation of each               |              |

|                                                                                                                 | 8-14         |

|                                                                                                                 | 8-14         |

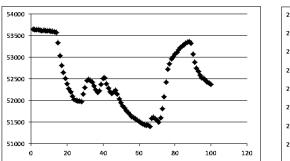

| Figure 8-13. Graphs of temperature variation in diodes D1 and D2. These graphs were obtained up an eyeal sheet  | _            |

|                                                                                                                 | 8-15         |

|                                                                                                                 | 8-15         |

| Figure 8-15. Video output of S3921-128Q MOS linear image sensor in the oscilloscope and conversions to be made. | Q_1 <i>C</i> |

| CONVENSIONS TO BE MIGUE:                                                                                        | 8-16         |

| Figure 8-16. An acquisition of MOS.                                                                           | 8-17 |

|---------------------------------------------------------------------------------------------------------------|------|

| Figure 8-17. Final prototype with MOS.                                                                        |      |

| Figure 8-18. Schematic with state buffer/line driver (ex.: HCT244).                                           |      |

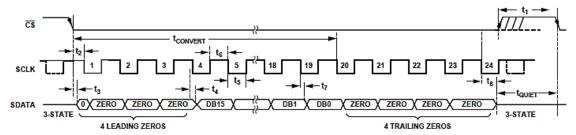

| Figure M-1. AD7680 Serial Interface Timing Diagram - 24SCLK Transfer.                                         | M    |

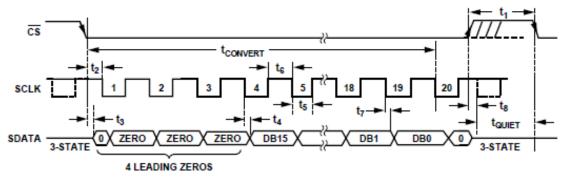

| Figure M-2. AD7680 Serial Interface Timing Diagram - 20 SCLK Transfer.                                        | M    |

|                                                                                                               |      |

| List of Tables                                                                                                |      |

| Table 3-1. LM78M05CT Specifications.[19]                                                                      | 3-3  |

| Table 3-2. Electrical characteristics of LD1085V50.[20]                                                       |      |

| Table 3-3. Input and Output specifications of IE1224S DC/DC Converter.[21]                                    |      |

| Table 3-4. Terminal functions of PTN78000A regulator.[23]                                                     |      |

| Table 3-5. Pin Function Descriptions of AD7680. [22]                                                          |      |

| Table 6-1. File extensions names in compilation driver                                                        |      |

| Table 6-2. Example of stored at address 0x100 of 32-bit value 0x12345678                                      |      |

| Table 6-3. Integer representation values in MPLAB C32 C Compiler.                                             |      |

| Table 6-4. MPLAB C32 C Compiler floating-point format                                                         |      |

| Table 8-1. Analysis of points converted by the ADC subjected to a potential of 1.3 volts.                     |      |

| Table 8-2. Analysis of one acquisition with 512 points, converted by the ADC subjected t of 1.3 volts.        | •    |

|                                                                                                               |      |

| Y' . CD                                                                                                       |      |

| List of Examples                                                                                              |      |

| Example 2-1. Code example will set group priority level                                                       | 2-2  |

| Example 2-2. Code example will set group sub priority level                                                   |      |

| Example 2-3. Code Example of Analog and digital inputs/outputs                                                |      |

| Example 2-4. 16-Bit Timer Interrupt Initialization Code Example                                               |      |

| Example 2-5. Timer ISR Code Example.                                                                          |      |

| Example 2-6. Example code for configuration of the single output pulse event and Interr (16-Bit Mode)         |      |

| Example 2-7. Example code for configuration of the continuous output pulse event and Servicing (16-Bit Mode). | -    |

| Example 8-1. Code for communication between two Windows Forms                                                 |      |

| Example 8-2. Partial code to display data in continuous mode                                                  |      |

| Example 8-3. Partial code for storage in .txt format                                                          |      |

| Example 8-4. Partial code that shows how values of parameters are sent to the PIC                             |      |

| Example 8-5. Partial code of MPLAB Firmware                                                                   |      |

| Example 8-6. Partial code used to send 512 conversions to PC                                                  |      |

| Example 8-7. Partial code used to make ADC conversions                                                        |      |

| Example 8-8.Example of PIC problem description.                                                               | 8-19 |

|                                                                                                               |      |

|                                                                                                               |      |

# Chapter 1. Introduction

#### 1.1 - Diabetic Neuropathy

Diabetic peripheral neuropathy (DPN) is nerve damage caused by diabetes, affects up to 50% of older type 2 diabetic patients and is the major cause of chronic disability in diabetic patients, being implicated in 50-75% of non-traumatic amputations. Patients with peripheral neuropathy must be considered at risk of insensate foot ulceration and must receive preventive education and care. [1]

The present approach to reduce diabetic neuropathy complications is based on its early diagnosis and accurate assessment, a difficult task due to the non-availability of a simple non-invasive method for early diagnosis. [2]

DPN is by far the most common of all the neuropathies and may be divided into the following two main types:

- Acute sensory neuropathy

- Chronic sensorimotor neuropathy

Acute sensory neuropathy is a distinct variety of the symmetrical polyneuropathies<sup>1</sup> with an acute or sub-acute onset characterized by severe sensory symptoms, usually with few if any clinical signs.

Chronic sensorimotor neuropathy is by far the most common form of DPN. It's usually of insidious onset and may be present at the diagnosis of type 2 diabetics in up to 10% of patients. Whereas up to 50% of patients with chronic DPN may be asymptomatic symptoms sufficient to warrant specific therapy. [3]

Management of diabetic neuropathy includes two approaches: therapies for symptomatic relief and those that may slow the progression of neuropathy. Of all treatments, tight and stable glycemic control is probably the most important for slowing the progression of neuropathy. [4]

The cornea is one of the most densely innervated tissues in the human body and is accessible to inspection through optical methods. In the past 15 years, several researches proposed the use of morphologic parameters extracted from images of the corneal subbasal nerve plexus, acquired *in vivo*, on conscious patients, using corneal confocal microscopy (CCM). [5]

#### 1.2 - NeuroCórnea

The NeuroCórnea has the purpose of early detection and monitoring of diabetic peripheral neuropathy by automatic analysis of the *in vivo* morphology of corneal sub-basal nerves. The technique will be based on dedicated instrumentation meant to be coupled to

<sup>&</sup>lt;sup>1</sup> Poluneuropathy is a neurological disorder that occurs when many nerves throughout the body malfunction simultaneously.

a standard slip lamp, a feature that will ease its adaptation by ophthalmologists and general practitioners. [5,6]

This thesis project has an application in respect of NeuroCórnea. It is therefore requested a construction of a system capable of measuring the density of light from a slit lamp.

#### 1.3 - Objective

This is a continuing project, initiated in 2010/2011, and aims to consolidate conceptually a prototype system to acquire/scan based on a PIC microcontroller and a USB interface. The goal is also the control with speed and resolution suitable for the acquisition of confocal images of the cornea provided by a camera attached to a slip lamp.

The aims to embody the following tasks:

- 1. Study the existing system and its main components

- 2. Survey of possible operational problems and limitations

- 3. Digital oscilloscope. Acquisition in real time (continuously)

- 4. Submission of a comprehensive proposal for implementation of the final prototype

- 5. Completing the hardware/firmware solution and implementation of graphical user interface (GUI) for the acquisition and control

- 6. Image acquisition and parameterization of the performance in terms of resolution, speed and sensitivity

- 7. Adaptation of firmware and software to other applications

#### 1.4 - Microcontrollers

Microcontrollers are smart chips, which has a processor, pin for input/output (I/O) and memory. By programming the microcontroller can control their output, with reference inputs or an internal program.

What differentiates the various types of microcontrollers is the amount of memory (program and data), processing speed, number of I/O pins, power, peripherals, architecture and instruction set.

First to all we need to differentiate a microcontroller of a microprocessor, easy terms to be confused but there is great difference between them.

Figure 1-1. Zilog Z80 - 8-bit microprocessor designed and sold by Zilog from July 1976. [7]

A microprocessor circuit is very complex, in the form of an integrated circuit, which can contain from a few thousand (Figure 1-1) to 7 million transistors (Pentium II). These transistors are the most diverse internal logic circuits, such as counters, registers, decoders and hundreds of others. These logic circuits are arranged in a complex manner, giving the microprocessor the ability to perform logical, arithmetic and control operations.[7]

A microcontroller is na integrated circuit that has na internal microprocessor and all peripherals essential to its operation, like:

- Program Memory usually an EPROM¹ type memory which stores the program information, ie, the microprocessor should execute.

- Data Memory usually a type memory RAM (Random Acess Memory), where the information will be stored data that the program will use, is usually used to store a value or a flag.

- I/O Device Selection is the communication of memory locations with the external pins of the microcontroller.

- Timers and Counters used to tell time or count events.

- Clock in some microcontrollers the clock signal generator is also coupled to the microprocessor, it has the function to synchronize all the events of a digital circuit.

- Interrupt Controller Device as the name implies, is the component that controls the interrupt request to the CPU.

#### 1.4.1 - PIC

PIC (Peripheral Interface Controller) is a family of microcontrollers manufactured by Microchip Technology® which process data of 8-bits, 16-bits and more recently 32-bits (our case). They have wide variety of models and internal peripherals, have high processing speed due to its Harvard architecture and RISC² instruction set (35 sets of instructions and 76 instructions), with resources for programming flash memory and EEPROM³. (See Chapter 2)

**Note**.: The PIC18F also process data of 32-bit, double type variables for example. What distinguishes the architectures is the  $ALU^4$ . In the PIC18 is 8bits, in the PIC24 16bit ALU and have a PIC32 32-bit ALU

<sup>&</sup>lt;sup>1</sup> EPROM (rarely EROM), or Erasable Programmable Read Only Memory is a type of memory chip that retains its data when its power supply is switched off. In other words, it is non-volatile.

<sup>&</sup>lt;sup>2</sup> RISC or Reduced Instruction Set Computer simplifies the processor by only implementing instructions that are frequently used in programs; unusual operations are implemented as subroutines, where the extra processor execution time is offset by their rare use.

<sup>&</sup>lt;sup>3</sup> EEPROM (also written E<sup>2</sup>PROM) stands for Electrically Erasable Programmable Read-Only Memory and is a type of non-volatile memory used in computers and other electronic devices.

<sup>&</sup>lt;sup>4</sup> Arithmetic and Logic Unit (ALU) is a digital circuit that performs arithmetic and logical operations.

#### 1.5 - Von Neumann Architecture

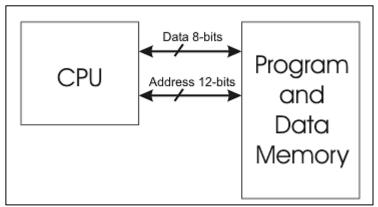

The Architecture of Von Neumann (Figure 1-2) is a computer architecture that is characterized by the possibility of a digital machine to store your programs on the same memory space as the data, thus being able to handle such programs. [8]

The Von Neumann architecture is used in microprocessor instructions which may have different formats, ie, the number of bytes used for writing the instructions may vary for instruction statement, and therefore, these microprocessors allows the use of a broad range instruction. CPUs are CISC (Complex Instruction Set Computer), suitable for software development highly structured and based on the use of repertoires of instructions that allows great design flexibility. [9]

Figure 1-2. The Von Neumann architecture. [10]

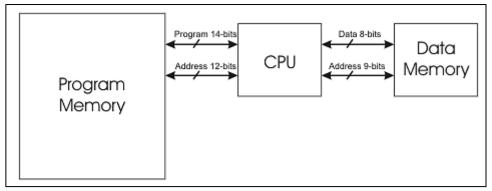

#### 1.6 - Harvard Architecture

The Harvard Architecture (Figure 1-3) based on a concept that the latest Von Neumann, and has been the need for the microcontroller to work faster. It's a computer architecture that distinguishes itself from others by having two different and independent memories in terms of bus and connection to the processor. It's based on the separation of bus and connection which are memories of the program instructions and data memories, allowing a processor can access both simultaneously, obtaining a better performance than the Von Neumann architecture, it may seek a new instructions while executing another. [11]

The Harvard Architecture is particularly suited for microprocessors that, by using a reduced number of instructions, are usually designated by RISC (Reduced Instruction Set Computer). [9]

Our PIC microcontroller family, which will be further specified in more detail, displays Harvard architecture and is designed in light of the RISC philosophy. For example, processors PIC16Fxxxx use a repertoire of thirty-five instructions written with words of fourteen bits, and operate on data words of eight bits.

Figure 1-3. The Harvard architecture. [10]

#### 1.7 - Modified Von Neumann Architecture and Harvard Architecture

Before closing this chapter, it should be noted that the distinction of slides based on the concept of philosophies CISC and RISC, or classification of the architecture, such as Harvard or Von Neumann, tends to blur as manufacturers of microprocessors increasingly betting more on developing devices whose architecture does not fit precisely those concepts. Often, these constructs are called "Modified Von Neumann Architecture" or "Modified Harvard Architecture" and display a repertoire of these microprocessors, instruction reinforced, ie a repertoire that, in addition to containing instructions, comprises instructions to a large processing capacity. [9]

For example, in some microcontrollers and in many microprocessors - signal processors of the type DSP (Digital Signal Processor) - often using a *Modified Harvard Architecture*, to allow the transfer of operands through the *bus*, at the outset, is dedicated to the program memory access, thus improving the performance of systems to perform operations on two operands that are involved.

# Chapter 2. PIC32 USB Starter Kit II Microchip

The PIC32 USB Starter Kit II (Figure 2-1) provides a method to experience the USB functionality of the PIC32 microcontroller. We can develop CAN (Controller Area Network) applications using PIC32 expansion board. With the board we can develop USB embedded host/device/OTG (USB On-The-Go) applications because it's possible combining this board with Microchip's free USB software. [12]

PIC32 USB Starter Kit II includes the following items:

- PIC32 USB Starter Kit II Development Board

- USB mini-B to full-sized A cable for debug.

- USB micro-B to full-sized A cable to communicate with the PIC32 USB port

- Three user-programmable LEDS

- Three push button switches

Figure 2-1. PIC32 USB Starter Kit II. [13]

**Note.:** The content (Figures and Examples) which are presented below, was adapted from "*PIC32MX Family Reference Manual*", for this reason there will be no other reference in this section (Chapter 2.1). This document is available on a CD-ROM that accompanies the PIC32 USB Starter Kit II and is available online on Microchip website. The intension of its inclusion was to provide the reader overall information of this important content for work project.

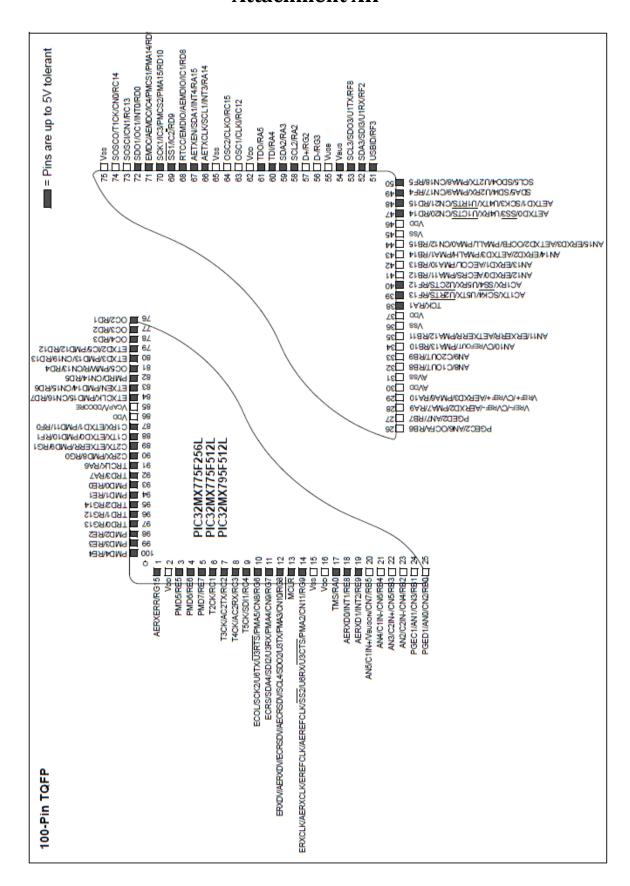

#### 2.1 - PIC32MX (PIC32MX795F512L)

The PIC32MX795F512L manipulation involves a huge knowledge of its architecture, its functional blocks and their components. There is no logic to explain everything about the PIC in this thesis; however, I will make a brief reference to the functional blocks of most interest.

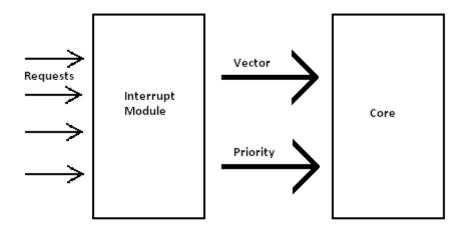

#### 2.1.1 - Interrupts

In response to interrupt events, PIC32MX795F512L generates interrupt request. The interrupts module includes the following (but not only) features:

- 96 interrupt sources

- 64 interrupt vectors

- Single and Multi-Vector mode operations

- 7 user-selectable priority levels for each vector

- 4 user-selectable sub priority levels within each priority

Figure 2-2. Interrupt Controller Module.

**Note**.: The *Attachment I* provide a brief summary of interrupt module registers.

#### 2.1.1.1 - Interrupt Priorities and Sub Priorities

We can select priority levels in range from 1 (low) to 7 (high). If an interrupt priority is "0", the interrupt vector is disabled.

The following code example will set the priority to level 2.

Example 2-1. Code example will set group priority level.

We can select a sub priority in range from 0 (low) to 3 (high). The following code example will set the sub priority to level2.

Example 2-2. Code example will set group sub priority level.

#### 2.1.2 - I/O Ports

I/O pins are considered the simplest of peripherals because. I/O pins allow monitor and control devices.

#### 2.1.2.1 - Control Registers

The I/O Ports module consists of the following Special Function Registers (SFRs):

- TRISx: Data Direction register for the module "x"

- PORTx: PORT register for the module "x"

- LATx: Latch register for the module "x"

- ODCx: Open-Drain Control register for the module "x"

**Note1**.: "x" denotes any port module instances

Note2.: The Attachment II provides a brief summary of all I/O ports-related registers.

#### 2.1.2.2 - Modes of Operation

I/O pins can be configured as:

- Digital Inputs (TRIS register bits = 1)

- Analog Inputs

- Digital Outputs (TRIS register bits = 0)

- Analog Outputs

- Open-Drain Configuration (ODCx register = 1)

Example 2-3 illustrates configuring RBO, RB1 as analog (default) inputs, RB2 as a digital input and RB4 as a digital output with open-drain enabled using SET, CLR atomic SFR registers.

Example 2-3. Code Example of Analog and digital inputs/outputs.

**Note**.: The *Attachment III* provides a summary of I/O pin mode settings configuration.

#### 2.1.3 - Timers

We can configure PIC32MX795F512L with two different types of timers:

#### Type A Timer

- 16-bit time

- Software selectable prescalers 1:1, 1:8, 1:64 and 1:256

#### Type B Timer

- 16-bit or 32-bit timer

- Software selectable prescalers 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64 and 1:256

**Note**.: 32-bit timer/counter configuration requires an even-numbered timer combined with an adjacent odd-numbered timer, e.g., Timer2 and Timer3, or Timer4 and Timer 5.

#### 2.1.3.1 - Control Registers

We configure a 16-bit timer with the following Special Function Registers (SFRs):

- TxCON: 16-Bit Control Register Associated with the Timer

- TMRx: 16-Bit Timer Count Register

- PRx: 16-Bit Period Register Associated with the Timer

- TxIE: Interrupt Enable Control Bit

- TxIF: Interrupt Flag Status Bit

- TxIP: Interrupt Priority Control Bits

- TxIS: Interrupt Subpriority Control Bits

**Note**.: The *Attachment IV* summarizes all Timer-related registers.

PIC32MX795F512L timer module has an interrupt flag bit TxIF, an interrupt mask bit TxIE and its priority level.

Example 2-4 will enable Timer2 interrupts, load the Timer2 Period register and starts the Timer. When a Timer2 period match interrupts occurs, the ISR must clear the Timer2 interrupt status flag in software.

Example 2-4. 16-Bit Timer Interrupt Initialization Code Example.

Example 2-5 demonstrates a simple ISR for Timer1 interrupts. The code at this ISR handler should perform any application specific operations and must clear the corresponding Timer1 interrupt status flag before exiting.

```

void __ISR(_Timer_1_Vector,ipl3)TimerlHandler(void)

{

... perform application specific operations in response to the interrupt

IFSOCLR = 0x00000010; // Be sure to clear the Timer 2 interrupt status

}

```

Example 2-5. Timer ISR Code Example.

#### 2.1.4 - Output Compare

PIC32MX795F512L output compare (OC) module is used to generate one single pulse or set of pulses.

Example 2-6 will set the OC1 module for interrupts on the single pulse event and select Timer2 as the clock source for the compare time base. Example 2-7 set the OC1 for continuous pulse event.

```

T2CON = 0x0010;

// Configure Timer2 for a prescaler of 2

OC1CON = 0x0000;

// Turn off OC1 while doing setup.

// Configure for single pulse mode

// Initialize primary Compare Register

OC1CON = 0x0004;

OC1R = 0x3000:

OC1RS = 0x3003:

// Initialize secondary Compare Register

PR2 = 0x3003;

// Set period (PR2 is now 32-bits wide)

// configure int

// Clear the OCl interrupt flag

IFSOCLR = 0 \times 000000040;

IFS0SET = 0 \times 000000040;

// Enable OC1 interrupt

// Set OC1 interrupt priority to 7,

IPC1SET = 0x001C0000;

// the highest level

IPC1SET = 0x00030000;

// Set Subpriority to 3, maximum

T2CONSET = 0x8000:

// Enable Timer2

OC1CONSET = 0x8000:

// Enable OC1

// Example code for Output Compare 1 ISR:

void__ISR(_OUTPUT_COMPARE_1_VECTOR, ip17) OC1_IntHandler (void)

// insert user code here

// Clear the OCl interrupt flag

IFSOCLR = 0x0040:

```

Example 2-6. Example code for configuration of the single output pulse event and Interrupt Servicing (16-Bit Mode).

```

T2CON = 0x0010:

// Configure Timer2 for a prescaler of 2

OC1CON = 0x00000;

// disable OC1 module

OC1CON = 0x0005;

// Configure OC1 module for Pulse output

OC1R = 0x3000;

// Initialize Compare Register 1

OC1RS = 0x3003:

// Initialize Secondary Compare Register 1

PR2 = 0x5000:

// Set period

// configure int

IFSOCLR = 0x00000040:

// Clear the OCl interrupt flag

IFS0SET = 0x00000040;

IPC1SET = 0x001C0000;

// Enable OCl interrupt

// Set OC1 interrupt priority to 7,

// the highest level

IPC1SET = 0x00030000;

// Set Subpriority to 3, maximum

T2CONSET = 0x8000;

// Enable Timer2

OC1CONSET = 0x8000;

// Enable OC1

// Example code for Output Compare 1 ISR:

void__ISR(_OUTPUT_COMPARE_1_VECTOR, ip17) OC1_IntHandler (void)

// insert user code here

IFSOCLR= 0x0040;

// Clear the OCl interrupt flag

```

Example 2-7. Example code for configuration of the continuous output pulse event and Interrupt Servicing (16-Bit Mode).

#### 2.1.4.1 - Output Compare Functions

This section contains a list of individual functions for Output Compare module and an example of use of the functions.

#### CloseOC1 . . . CloseOC5

This function disables the Output Compare interrupt and then turns off the module. The Interrupt Flag bit is also cleared.

```

Code Example: CloseOC1();

```

#### ConfigIntOC1 . . . ConfigIntOC5

This function clears the Interrupt Flag bit and then sets the interrupt priority and enables/disables the interrupt.

```

Interrupt enable/disable:

OC_INT_ON

OC_INT_OFF

Interrupt Priority:

OC_INT_PRIOR_0 . . . OC_INT_PRIOR_7

Interrupt Sub-priority:

OC_INT_SUB_PRIOR_0 . . . OC_INT_SUB_PRIOR_3

Code Example: ConfigIntOC1(OC_INT_ON | OC_INT_PRIOR_2 | OC_INT_SUB_PRIOR_2);

```

#### OpenOC1 . . OpenOC5

This function configures the Output Compare Module Control register (OCxCON) with the following parameters: Clock select, mode of operation, operation in Idle mode. It also configures the OCxRS and OCxR registers.

```

Module on/off control:

OC_ON

OC_OFF

Clock select:

OC_TIMER2_SRC

OC_TIMER3_SRC

Output Compare modes of operation:

OC_PWM_FAULT_PIN_ENABLE

OC_PWM_FAULT_PIN_DISABLE

OC_CONTINUE_PULSE

OC_SINGLE_PULSE

OC_TOGGLE_PULSE

OC_HIGH_LOW

OC_LOW_HIGH

OC_MODE_OFF

```

<u>Code Example</u>: OpenOC1(OC\_ON | OC\_TIMER2\_SRC | OC\_PWM\_FAULT\_PIN\_ENABLE, 0x80, 0x60);

#### 2.2 - I/O Expansion Board

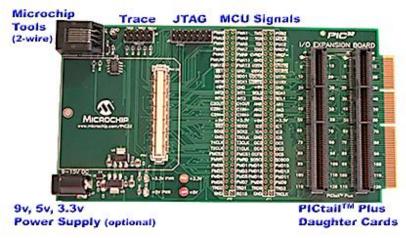

The Starter Kit I/O Expansion Board provides full access to MCU signals, additional debug headers and connections of PICtail™ Plus daughters boards. MCU signals are available to attaching prototype circuits or monitoring signals with logic probes. [14]

Figure 2-3. The Starter Kit I/O Expansion Board.[14]

To make the connections of external devices to the PIC we use a daughter board to solder the wires and devices required. The advantage of having a daughter board is its portability, ie, it is not necessary to remove the PIC development board for soldering wires, another advantage is that perhaps if something goes wrong, we know that all connections are being made to from the daughter board, so it is easier to discover the provenance of the breakdown.

Figure 2-4. Microchip PICtail Plus Daughter Board.

**Note.:** The pin out equivalence of the development board for the daughter board is shown in Attachment XI.

# **Chapter 3.** Power Supply Voltage Board

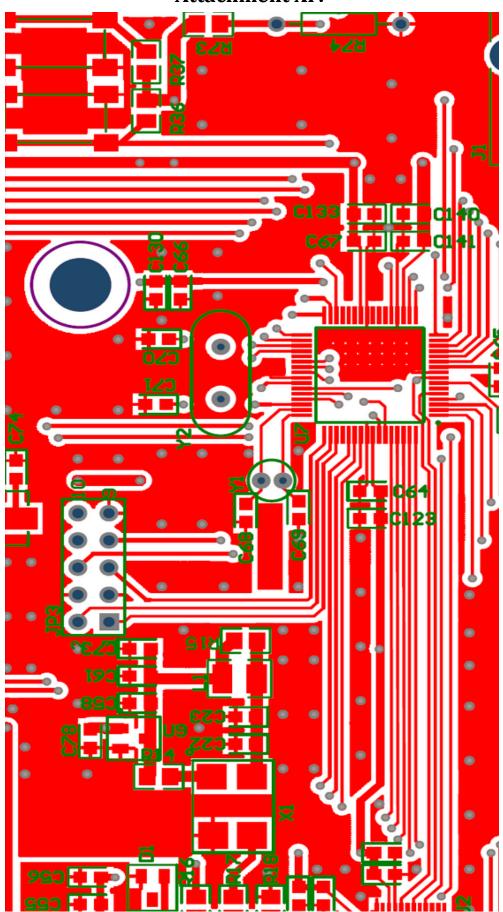

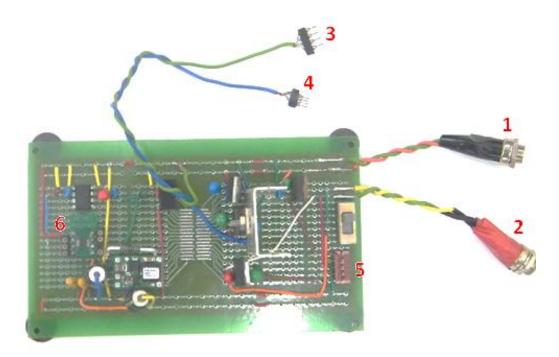

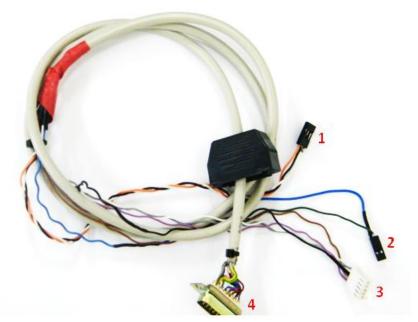

The power board in Figure 3-1 was built entirely by us. This board has the function to supply all components of our system and has two power inputs (1 and 2).

This board also has an ADC and communication with PIC is made by SPI. (See Attachment XIII)

Figure 3-1. Board with power supplies for the Hamamatsu FFT-CCD C5809 Image Sensor

#### Legend of Figure 3-1:

- 1 XP Power, model AED100US19 that provides +19 V DC output of power (Input)

- 2 ELECTRO DH, model 50.055 that provides +6.5V DC output of power (Input)

- 3 -GND

- 4 +5V (PIC supply)

- 5 GND, +5, +15, -15, +24 Volts (Output)

- 6 16-bit ADC AD7680

**Note**.: 6.5 V input is required for LD1085V50 regulator because dropout is guaranteed at a maximum of 1.2 V at the maximum output current. Experimentally it was found that when we supply the regulator with 19V, 15V or 12V it was very hot and damaged. Moreover, we needed current of about 2A to the FFT-CCD and we could not maintain the 5V regulator.

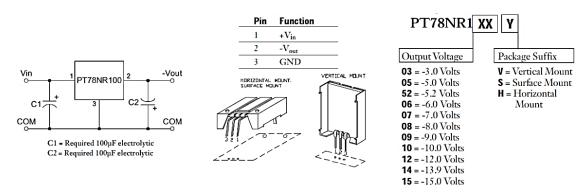

#### 3.1 - PT78NR115S (-15V)

The PT78NR115S (Figure 3-2) creates a negative output voltage (-15V) from a 12V of input voltage with maximum output power of 5 watts. [16]

Figure 3-2. Standart Application, Pin-Out Information and Ordering Information of PT78NR100 Series.

[16]

## 3.2 - L7812CV (+12V)

The L7812CV of three-terminal positive regulator (Figure 3-3) creates a positive output voltage (+12V) from a +19V of input voltage and can deliver over 1A output current. [17]

Figure 3-3. Connection Diagram (top view) and Standart Application Circuits of the L7800 series regulators.[17]

#### 3.3 - LM7815CV (+15V)

The LM7815CV is available in an aluminum TO-3<sup>1</sup> package (Figure 3-4) which will allow over 1.0A load current if adequate heat sinking is provided and creates a positive output voltage (+15V) from +12 of input voltage. [18]

<sup>&</sup>lt;sup>1</sup>TO-3 ("transistor outline") is a designation for a standardized metal semiconductor package used for transistors and some integrated circuits.

Figure 3-4. Connection Diagram (top view) and Standart Application Circuits of the LM7800 series regulators.[18]

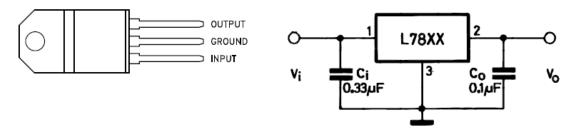

## 3.4 - LM78M05CT (+5V)

The LM78M05CT of three-terminal positive voltage regulator (Figure 3-5) creates a positive output voltage (+5V) from positive input voltage [19]

| Unless othe         | rwise specified: $V_{IN} = 10V$ , $C_{IN} = 0$ | ).33 μF, C <sub>O</sub> = 0.1 μF     |                         |      |     |      |         |                       |

|---------------------|------------------------------------------------|--------------------------------------|-------------------------|------|-----|------|---------|-----------------------|

| Symbol              | Parameter                                      | Condition                            | าร                      | Min  | Тур | Max  | Units   |                       |

| Vo                  | Output Voltage                                 | I <sub>L</sub> = 500 mA              |                         | 4.8  | 5.0 | 5.2  | ٧       | ` } ()ૄ\${            |

|                     |                                                | 5 mA ≤ I <sub>L</sub> ≤ 500 mA       |                         | 4.75 | 5.0 | 5.25 |         |                       |

|                     |                                                | $P_D \le 7.5W, 7.5V \le V_{IN}$      | ≤ 20V                   |      |     |      |         | f                     |

| V <sub>R LINE</sub> | Line Regulation                                | $7.2V \le V_{IN} \le 25V$            | I <sub>L</sub> = 100 mA |      |     | 50   | mV      | 1                     |

|                     |                                                |                                      | I <sub>L</sub> = 500 mA |      |     | 100  | 1       |                       |

| V <sub>R LOAD</sub> | Load Regulation                                | 5 mA ≤ I <sub>L</sub> ≤ 500 mA       |                         |      |     | 100  | 1       |                       |

| l <sub>o</sub>      | Quiescent Current                              | I <sub>L</sub> = 500 mA              |                         |      | 4   | 10.0 | mA      |                       |

| ΔlQ                 | Quiescent Current Change                       | 5 mA ≤ I <sub>L</sub> ≤ 500 mA       |                         |      |     | 0.5  |         | \                     |

|                     |                                                | $7.5V \le V_{IN} \le 25V, I_{L} = 9$ | 500 mA                  |      |     | 1.0  |         |                       |

| V <sub>n</sub>      | Output Noise Voltage                           | f = 10 Hz to 100 kHz                 |                         |      | 40  |      | μV      |                       |

| $\Delta V_{IN}$     | Ripple Rejection                               | f = 120 Hz, I <sub>L</sub> = 500 m   | A                       |      | 78  |      | dB      |                       |

| ΔVO                 |                                                |                                      |                         |      | 10  |      | ub      |                       |

| V <sub>IN</sub>     | Input Voltage Required                         | I <sub>L</sub> = 500 mA              |                         | 7.2  |     |      | ٧       |                       |

|                     | to Maintain Line Regulation                    |                                      |                         |      |     |      |         | OUTPU<br>GND<br>INPUT |

| ΔVo                 | Long Term Stability                            | I <sub>L</sub> = 500 mA              |                         |      |     | 20   | mV/khrs | 7 2                   |

|                     |                                                |                                      |                         |      |     |      |         |                       |

Figure 3-5. Connection Diagram of the LM78M05CT regulator.[19]

Table 3-1. LM78M05CT Specifications.[19]

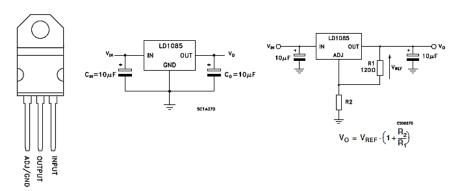

## 3.5 - LD1085V50 (+5V)

The LD1085V50 is a low drop voltage regulator (Figure 3-6) able to provide up to 3 A of output current. Dropout is guaranteed at a maximum of 1.2 V at the maximum output current, decreasing at lower loads. Only a 10  $\mu F$  minimum capacitor is need for stability and creates a positive output voltage (+5V) from ELECTRO DH, model 50.055 that provides +6.5V DC output. [20]

Figure 3-6. Pin Configuration (top view) and Application Circuit of the LD1085V50 regulator.[20]

| Symbol                                | Parameter                              | Test condition                                                                            | Min. | Тур.  | Max. | Unit |

|---------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------|------|-------|------|------|

| W                                     | Output voltage (1)                     | $I_O = 0$ mA, $T_J = 25$ °C                                                               | 4.95 | 5     | 5.05 | ٧    |

| Vo                                    | Output voltage (**)                    | I <sub>O</sub> = 0 to 3 A, V <sub>I</sub> = 6.6 to 30 V                                   | 4.9  | 5     | 5.1  | ٧    |

| 41/                                   | 12 1.2                                 | $I_O = 0$ mA, $V_I = 6.6$ to 20 V, $T_J = 25^{\circ}C$                                    |      | 0.5   | 10   | mV   |

| ΔV <sub>O</sub>                       | Line regulation                        | I <sub>O</sub> = 0 mA, V <sub>I</sub> = 6.6 to 20 V                                       |      | 1     | 10   | mV   |

| 41/                                   | Land annulation                        | I <sub>O</sub> = 0 to 3 A, T <sub>J</sub> = 25°C                                          |      | 5     | 10   | mV   |

| ΔV <sub>O</sub>                       | Load regulation                        | I <sub>O</sub> = 0 to 3 A                                                                 |      | 10    | 35   | mV   |

| $V_d$                                 | Dropout voltage                        | I <sub>O</sub> = 3 A                                                                      |      | 1.3   | 1.5  | ٧    |

| l <sub>q</sub>                        | Quiescent current                      | V <sub>I</sub> ≤ 30 V                                                                     |      | 5     | 10   | mA   |

|                                       | Short circuit current                  | $V_I - V_O = 5 V$                                                                         | 3.2  | 4.5   |      | Α    |

| I <sub>sc</sub> Short circuit current |                                        | V <sub>I</sub> - V <sub>O</sub> = 25 V                                                    | 0.2  | 0.5   |      | Α    |

|                                       | Thermal regulation                     | T <sub>A</sub> = 25°C, 30 ms pulse                                                        |      | 0.008 | 0.04 | %/W  |

| SVR                                   | Supply voltage rejection               | $f = 120 \text{ Hz}, C_O = 25 \mu\text{F}, I_O = 3 \text{ A} $ $V_I = 10 \pm 3 \text{ V}$ | 60   | 72    |      | dB   |

| eN                                    | RMS output noise voltage (% of $V_O$ ) | T <sub>A</sub> = 25°C, f = 10 Hz to 10 kHz                                                |      | 0.003 |      | %    |

| S                                     | Temperature stability                  |                                                                                           |      | 0.5   |      | %    |

| S                                     | Long term stability                    | T <sub>A</sub> = 125°C, 1000 Hrs                                                          |      | 0.5   |      | %    |

Table 3-2. Electrical characteristics of LD1085V50.[20]

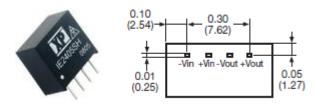

# 3.6 - IE1224S (+24V)

The IE1224S reference provides +24V DC output from +12V input voltage.

Figure 3-7. Image and pinout of IE1224S DC/DC Converter.[21]

| Input<br>Voltage <sup>ra</sup> | No Load<br>Input Current | Output<br>Voltage | Output<br>Current | Efficiency | Model Number <sup>g,a</sup> |

|--------------------------------|--------------------------|-------------------|-------------------|------------|-----------------------------|

|                                | 16 mA                    | 3.3 V             | 300 mA            | 72%        | IE1203S                     |

|                                | 16 mA                    | 5.0 V             | 200 mA            | 75%        | IE1205S                     |

| 12 VDC                         | 16 mA                    | 9.0 V             | 111 mA            | 77%        | IE1209S                     |

| 12 000                         | 16 mA                    | 12.0 V            | 84 mA             | 78%        | IE1212S                     |

|                                | 16 mA                    | 15.0 V            | 66 mA             | 78%        | IE1215S                     |

|                                | 16 mA                    | 24.0 V            | 42 mA             | 78%        | IE1224S                     |

Table 3-3. Input and Output specifications of IE1224S DC/DC Converter.[21]

This component was used in place of the PT78NR115S (there is no longer for sale).

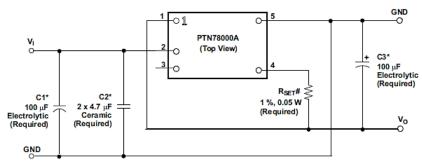

Operating from a wide-input voltage range, the PTN78000A provides high-efficiency, positive-to-negative voltage conversion for loads of up to 1.5 A. The output voltage is set using a single external resistor, and may be set to any value within the range, -15V to -3V (Table 3-4). [23]

Figure 3-8. Standard Application of PTN78000A regulator. Application Information in Attachment V.[23]

| TERMINAL              |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |

| v <sub>o</sub>        | 1   | 0   | The negative output voltage power node with respect to the GND node. It is also the reference for the $V_O$ Adjust control inputs.                                                                                                                                                                                                                                                                           |

| VI                    | 2   | - 1 | The positive input voltage power node to the module, which is referenced to common GND.                                                                                                                                                                                                                                                                                                                      |

| N/C                   | 3   |     | This pin is active and must be isolated from any electrical connection.                                                                                                                                                                                                                                                                                                                                      |

| V <sub>O</sub> Adjust | 4   | ı   | A 1% resistor must be connected between pin 1 and pin 4 to set the output voltage of the module lower than –3 V. If left open-circuit, the output voltage defaults to –3 V. The temperature stability of the resistor should be 100 ppm/°C (or better). The set-point range is –15 V to –3 V. The standard resistor value for a number of common output voltages is provided in the application information. |

| GND                   | 5   | I/O | The common ground connection for the $V_I$ and $V_O$ power connections.                                                                                                                                                                                                                                                                                                                                      |

Table 3-4. Terminal functions of PTN78000A regulator.[23]

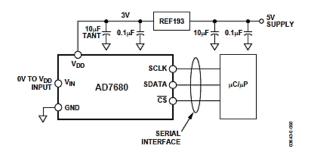

#### 3.7 - REF 195

In fact, because the supply current required by the 16-bit AD7680 is so low, a precision reference can be used as the supply source to the AD7680. REF195 (Figure 3-9) can be used to supply the required voltage to the ADC AD7680. This configuration is especially useful if the power supply available is quite noisy.

Figure 3-9. Typical Connection Diagram of the REF195. [22]

The AD7680 is a 16-bit, fast, low power, successive approximation ADC. The part operates from a single 2.5 V to 5.5 V power supply and features throughput rates up to 100 kSPS. [22]

The conversion process and data acquisition are controlled using CS<sup>1</sup> and the serial clock, allowing the devices to interface with microprocessors or DSPs<sup>2</sup>. The input signal is sampled on the falling edge of CS and the conversion is also initiated at this point. (Attachment XIII)

The reference for the part is taken internally from VDD, which allows the widest dynamic input range to the ADC. Thus, the analog input range for this part is 0 V to VDD. [22]

Figure 3-10. Functional Block Diagram and Pin Configuration of 16-Bit AD7680. [22]

| Pin No. | Mnemonic       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Voo            | Power Supply Input. The V <sub>DD</sub> range for the AD7680 is from 2.5 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                                                  |

| 2, 3    | GND            | Analog Ground. Ground reference point for all circuitry on the AD7680. All analog input signals should be referred to this GND voltage.                                                                                                                                                                                                                                                                                                               |

| 4       | V <sub>N</sub> | Analog Input. Single-ended analog input channel. The input range is 0 V to Vpo.                                                                                                                                                                                                                                                                                                                                                                       |

| 5       | SCLK           | Serial Clock. Logic input. SCLK provides the serial clock for accessing data from this part. This clock input is also used as the clock source for the AD7680's conversion process.                                                                                                                                                                                                                                                                   |

| 7       | SDATA          | Data Out. Logic output. The conversion result from the AD7680 is provided on this output as a serial data stream. The bits are clocked out on the falling edge of the SCLK input. The data stream from the AD7680 consists of four leading zeros followed by 16 bits of conversion data that are provided MSB first. This will be followed by four trailing zeroes if CS is held low for a total of 24 SCLK cycles. See the Serial Interface section. |

| 8       | ত্ত            | Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7680 and framing the serial data transfer.                                                                                                                                                                                                                                                                                              |

| 6       | NC             | No Connect. This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 3-5. Pin Function Descriptions of AD7680. [22]

<sup>2</sup> DSP or digital signal processor is a specialized microprocessor with an architecture optimized for the fast operational needs of digital signal processing.

<sup>&</sup>lt;sup>1</sup> Chip select (CS) or slave select (SS) is the name of a control line in digital electronics used to select one chip out of several connected to the same computer bus usually utilizing the three-state logic.

## Chapter 4. Hamamatsu Image Sensors

**Datasheets Information**

**Note**.: This chapter is an adaptation of information obtained in each equipment manual (referenced in the bibliography) and introduces the equipment to the reader before analyzing results.

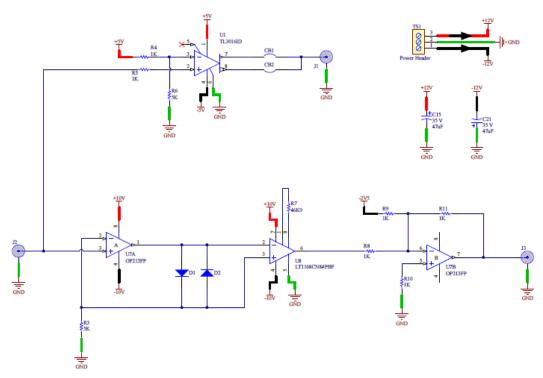

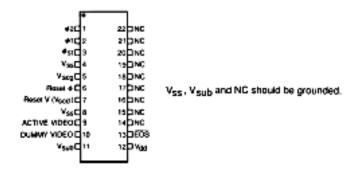

### 4.1 - FFT-CCD C5809 Image sensor

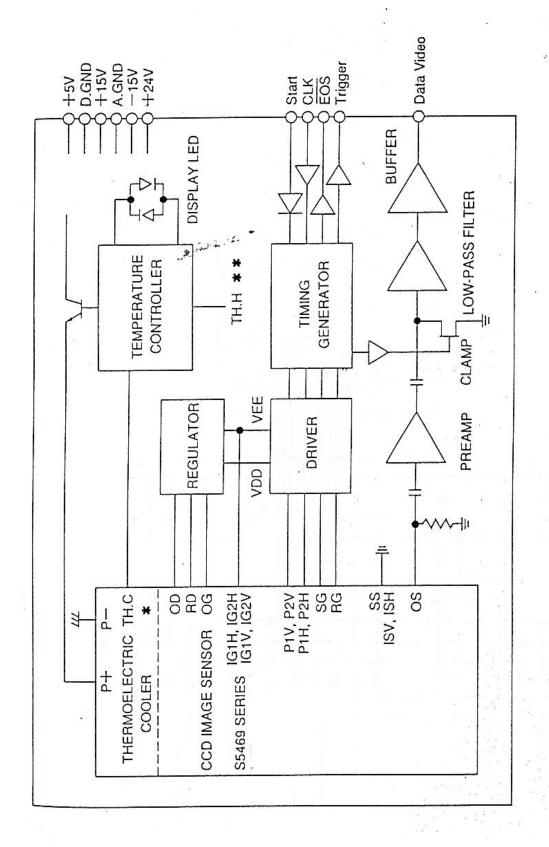

The C5809 series multichannel detector head consists of a thermoelectrically-cooled FFT-CCD image sensor, a low-noise driver/amplifier circuit and a temperature control circuit. This combination enables stable operation of the image sensor by input of simple external signals. [29]

The driver/amplifier circuit provides various timing signals necessary to operate the image sensor and processes the analog video signal from the image sensor with a low degree of noise. This circuit operates from two kinds of external control signals (Start, CLK) and four different supply voltages (+5V, +15V, -15V, +24V). (See Chapter 3)

#### 4.1.1 - Timing signal generator

Consisting of a counter and EPROM, the timing signal generator supplies various timing signals. It also provides trigger signals (Trigger) for external A/D conversion (See Attachment XIII). These signals are synchronized with external master clock pulse signals (CLK) and initialized by start pulse signals (Start).

#### 4.1.2 - Voltage regulators

The voltage regulator generates various voltages necessary to operate the image sensor. Each voltage is generated by a low noise regulator with a high degree of accuracy and stability. (See Chapter 3)

Note1.: For operating procedures see Attachment VII

**Note2**.: If "Green" LED is ON, indicates that the cooling temperature is set to the present level (TS = 0 °C). If "Red" LED is ON, warns that overheat is occurring due to electrical open or short circuit of the thermistor in the image sensor, or failure of the thermoelectric cooler. In this case we immediately turn the power off.

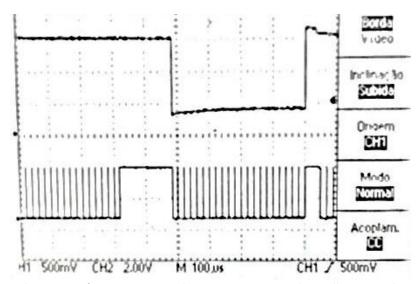

Inputting two kinds of control signals (Start, CLK) from the PIC to the driver/amplifier circuit. The pulse width of the "Start" signal must be longer than one cycle of the "CLK" signal, and should be synchronized with the "CLK" signal as much as possible.

The "CLK" signal frequency determines the readout frequency of the "Data Video" signal, and the pulse interval of the "Start" signal determines the storage time to the image sensor.

#### Using the FFT-CCD image sensor operated at "CLK" signal frequency of 1MHz:

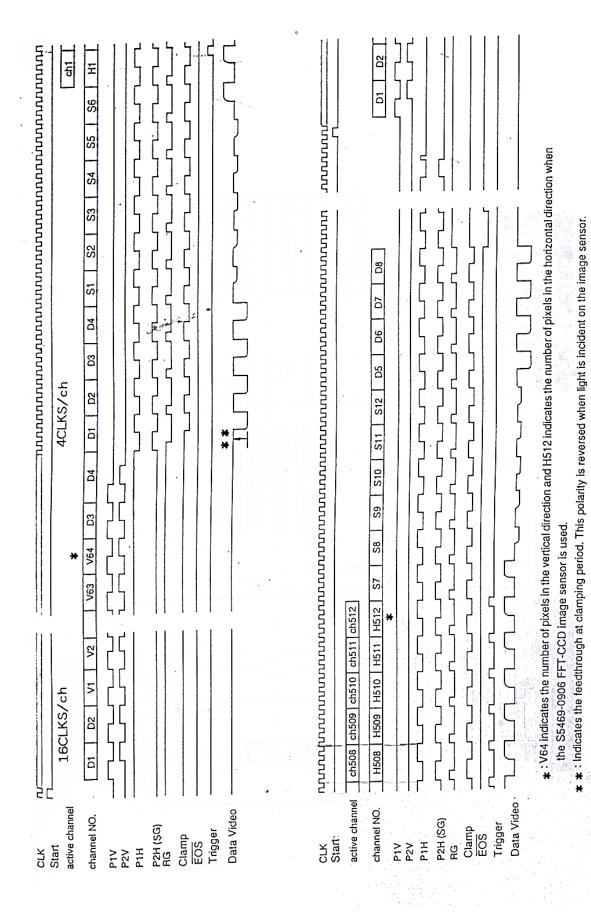

The readout frequency for the "Data Video" signal is 1/4<sup>th</sup> the "CLK" signal frequency (See Attachment VII). The readout time per one channel, *tv*, is 4us.

The binning operation frequency is 1/16<sup>th</sup> the "CLK" signal frequency. The binning operation time per one channel, *tb*, is 16us.

Thus, the time required for one scan, *tscan*, including the binning operation time becomes

$$t_{scan} = t_v \times N_h + t_b \times N_{hv} = 4\mu s/ch \times 532 + 16\mu s/ch \times 68 = 3.216ms$$

= 3216 periodos de CLK

Equation 4-1. Time required for one scan of the FFT-CCD image sensor.

Where:

Nv – Number of channels of the vertical register.

Nh - Number of channels of the horizontal register.

Note.: See Attachment VIII

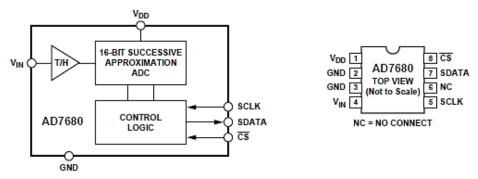

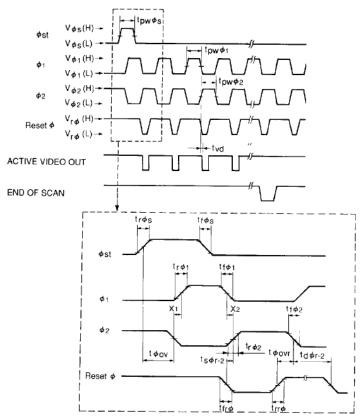

#### 4.2 - S3921-128Q MOS Linear Image Sensor

The S3921 MOS linear image sensor feature a signal processing circuit which integrates a signal charge in the inner video line and performs impedance conversion to provide an output signal with a boxcar waveform. This allows signal readout with a simple external circuit. The S3921 also have a wide photosensitive area with a pixel height of 2.5mm and a pixel pitch of  $50\mu m$ . [28]

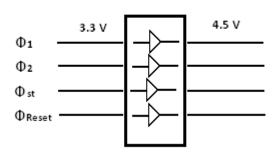

#### 4.2.1 - Driver Circuit

Driving the MOS shift register requires a start pulse ( $\phi$ st) and two.phase clock pulses ( $\phi$ 1,  $\phi$ 2). The polarities of  $\phi$ st,  $\phi$ 1 and  $\phi$ 2 are positive.  $\phi$ 1 and  $\phi$ 2 can be either fully separated or in the complementary relation. However, the overlap should not exist at the rise or fall edge between  $\phi$ 1 and  $\phi$ 2. In other words,  $\phi$ 1 and  $\phi$ 2 must not be at the high

level at the same time. The pulsewidth of  $\phi 1$  and  $\phi 2$  must be longer than 200 ns. Since the photodiode signal is obtained at the rise of every  $\phi 2$ , the clock pulse frequency determines the video data rate. [28]